Tien Shen

About Me

Hi, I’m Tien 👋. I’m an engineer with a passion for building systems, exploring embedded software, and creating cool side projects. This site is my personal portfolio where I showcase the things I’ve built and worked on.

Projects

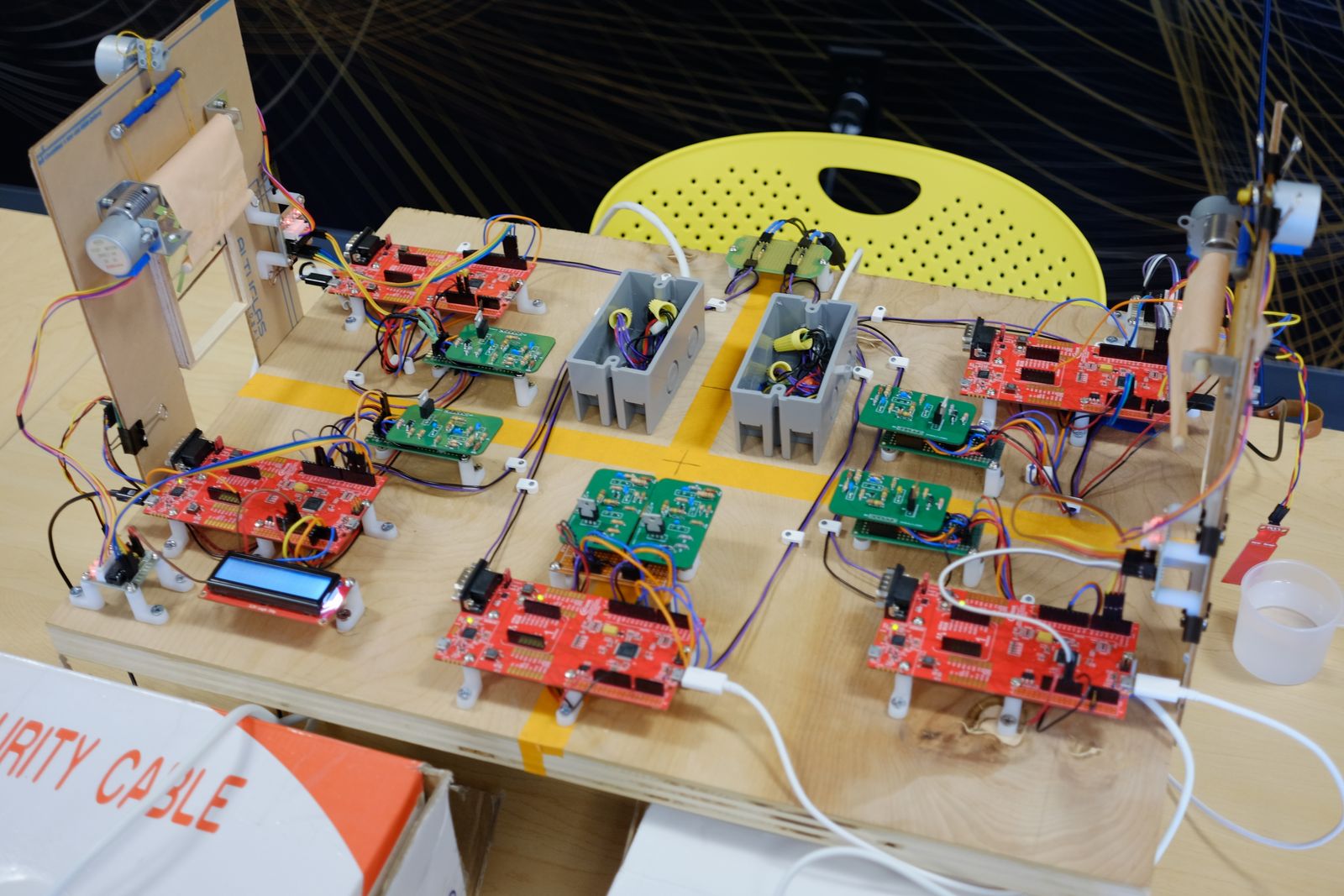

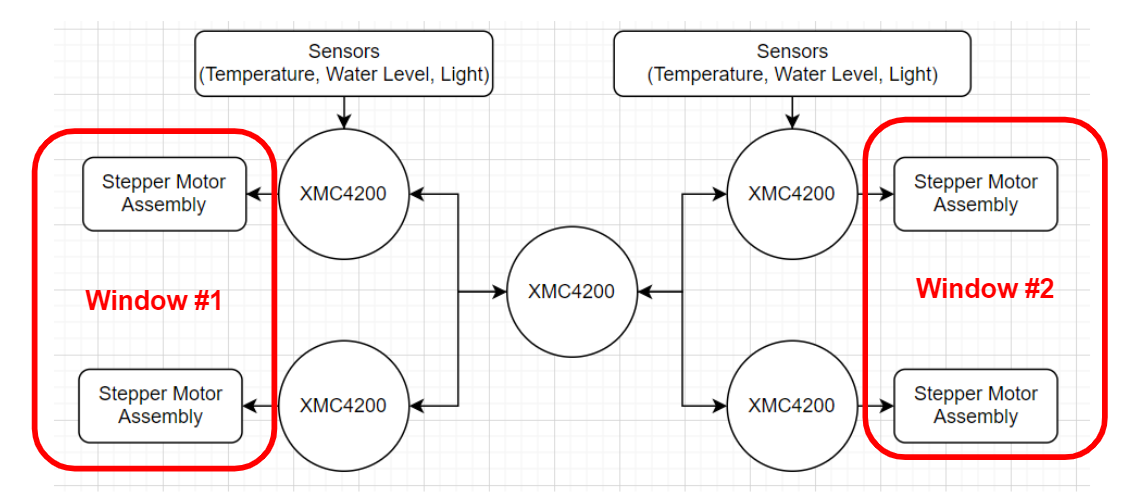

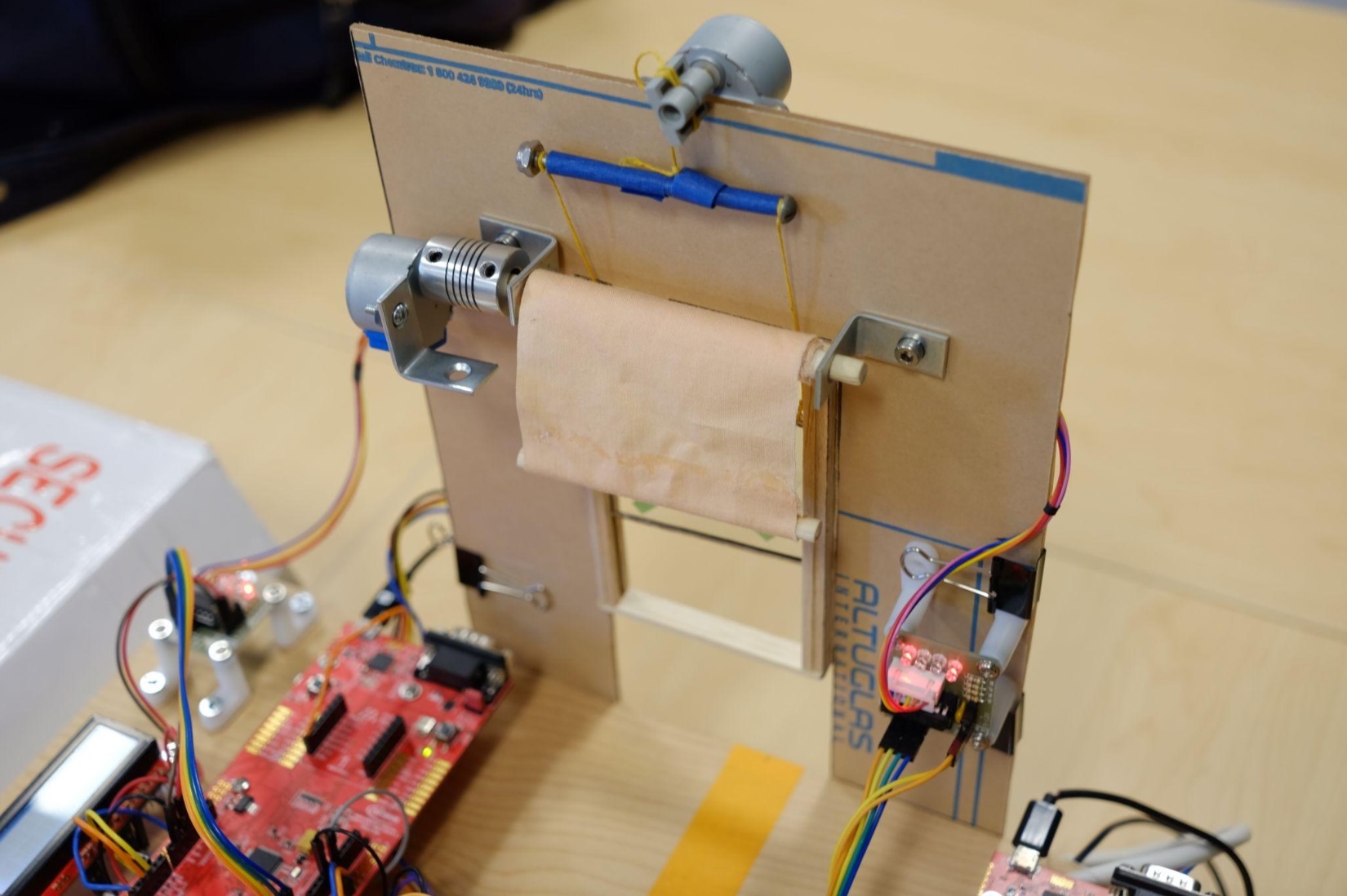

Active Window – UMass Senior Design Project

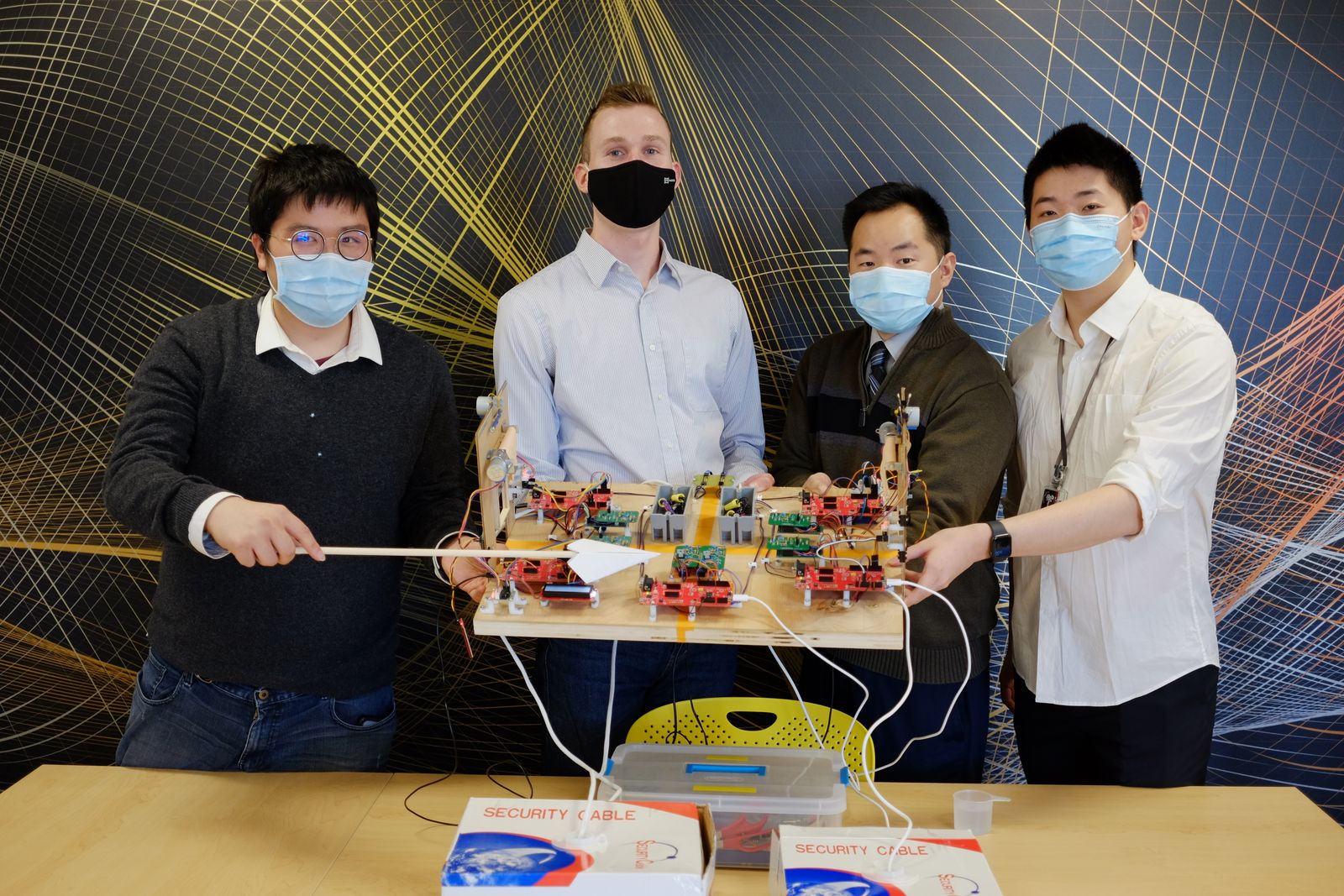

UMass Team 15: Tien Shen, Nathan Johnson, Michael Chan, Dingbang Chen

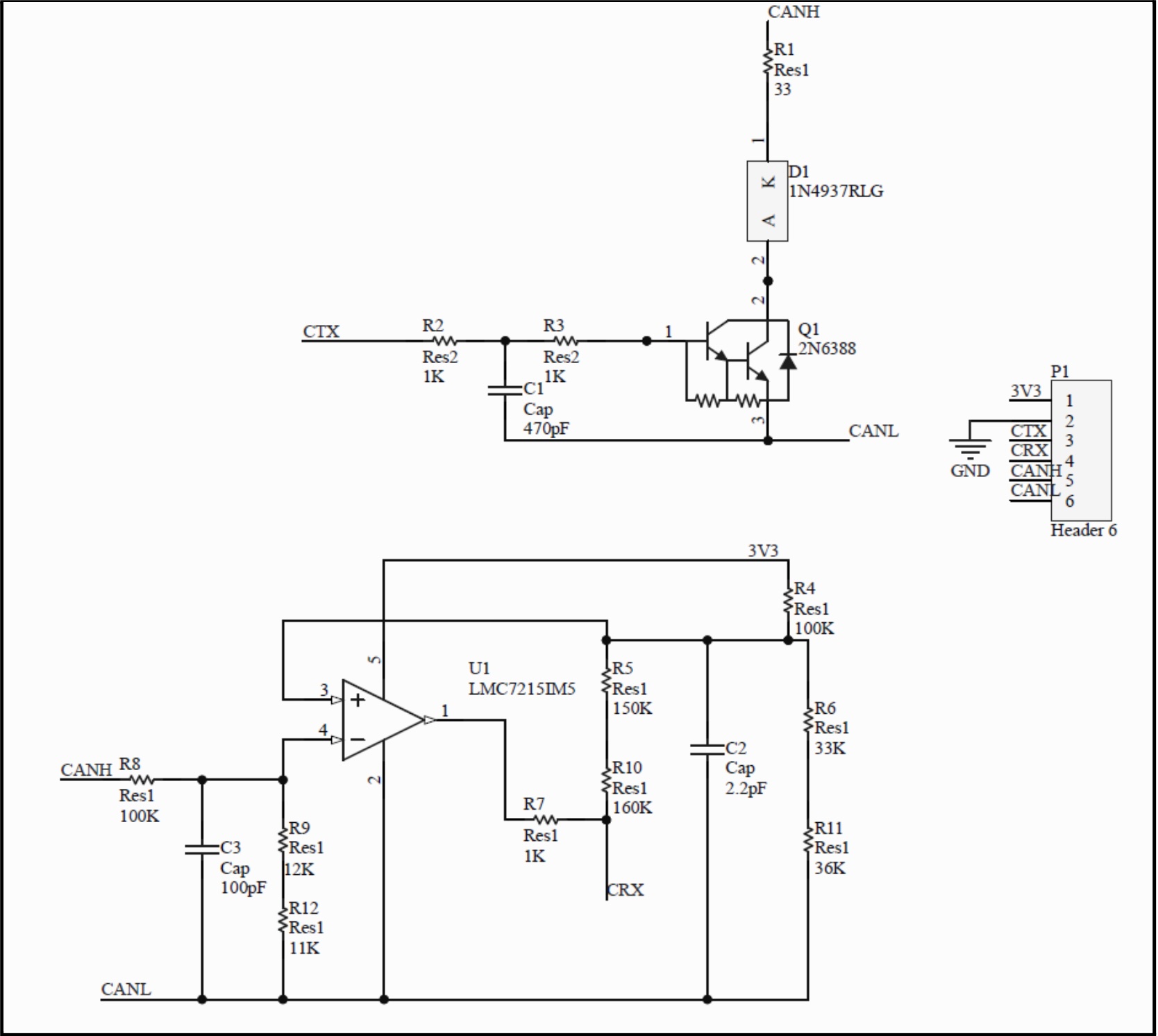

Developed an open-source software framework and CAN transceiver circuit for smart building networks. Prototype used Infineon XMC4200 boards, sensors, actuators, and custom window models to demonstrate a scalable, energy-efficient smart home system.

- C/C++ for embedded software

- CAN bus protocol

- Infineon XMC4200 microcontrollers

- Custom PCB design

Multi-threaded HTTP Server

High-performance HTTP server developed in C++ with collaborative graduate-level research. Implemented comprehensive support for HTTP requests, JPEG image serving, and error handling with multi-threading architecture for concurrent client connections.

- C++ & POSIX threads programming

- Socket programming (TCP/IP)

- HTTP protocol & JPEG image serving

- Performance benchmarking vs Apache HTTP server

- Concurrent client handling & error management

This Website (Portfolio)

Personal portfolio built with Next.js (app router), Tailwind CSS and TypeScript. Features a theme toggle with smooth transitions, responsive layout, and project showcase.

- Next.js 15 with App Router

- TypeScript & Tailwind CSS

- Dark/Light theme toggle

- CSS custom properties & transitions

Kaggle ML Competition: Mechanism of Action Prediction

Machine learning project focused on predicting biological mechanisms of action from gene expression and cell viability data. Applied dimensionality reduction and ensemble methods to classify drug responses across multiple targets.

- Principal Component Analysis (PCA)

- Ridge & Logistic Regression

- AdaBoost & Random Forest

- Multilayer Perceptron (MLP)

SRAM Cache Design Project

Complete VLSI design flow project from specification to physical layout. Implemented SRAM cache using industry-standard EDA tools, demonstrating full chip design methodology from RTL to GDSII.

- OpenRAM with NCSU FreePDK 45nm

- Verilog RTL with OpenCache

- Synopsys Design Compiler synthesis

- Cadence Encounter P&R

VLSI Bit Accumulator

Custom IC design project featuring a bit accumulator circuit in 45nm technology. Complete analog/digital design flow including schematic capture, physical layout, and comprehensive verification with timing and power analysis.

- Virtuoso Schematic Editor design

- 12.5µm × 3.7µm layout (45nm)

- HSPICE simulation & verification

- Frequency & power characterization

Professional Experience

Systems Engineer II

RTX | Raytheon Missiles and Defense

- • Served as Safety Representative on new system concept proposals of the Patriot SAM system, including the Warfighter Machine Interface, Radar Surveillance, Guidance, Command and Control, and Tactical Initialization

- • Analyzed 170+ Software Investigation Reports, 110+ safety-critical software updates, and 40+ system requirement changes—identifying over 30 potential safety hazards

- • Collaborated with safety, systems, and validation engineers to produce and deliver a comprehensive Patriot Safety Assessment Report to customers, in compliance with Military Standards 882E

DDRIO Pre-Silicon Design Verification Intern

Intel Corporation

- • Implemented UVM monitor and checker in SystemVerilog to validate DLL phase power optimization features across 30 instantiations in DDRIO, enabling a new power-saving feature to be released on the next-gen Intel server processor

- • Contributed to CI/CD initiatives by optimizing regression test sets, improving test execution efficiency, and streamlining the testing-release pipeline to accelerate delivery without compromising quality

- • Developed a Python tool to compare register specs between source code and Excel files, identifying over 200 discrepancies used across RTL, validation, and analog teams

Graduate Research Assistant

Reconfigurable Computing Group, UMass Amherst

- • Collaborated with a team of 4 graduate students to formally verify the open-source Symbiflow FPGA toolchain and delivered the software product to our sponsor

- • Implemented software changes and scripts to formally verified Yosys hardware synthesis software with Cadence Conformal LEC on 120 benchmark designs

- • Verified 21 benchmark designs synthesized by open-source software Yosys functioning on the FPGA development board and equivalent to commercial software Xilinx Vivado simulation using synthesizable RTL test harness

Education

Master of Science in Computer Engineering

University of Massachusetts Amherst

Riccio College of Engineering

May 2023Relevant Coursework:

Bachelor of Science in Computer Engineering

University of Massachusetts Amherst

Riccio College of Engineering

May 2021Foundation Coursework:

Contact

Feel free to reach out! You can contact me via email attimshen1999@gmail.com